Linux系统下开发C语言程序使用的gcc编译器,编译过程一般由Makefile脚本结合make程序实现. 基于Makefile脚本的编译过程自动化, 只要在终端输入make命令, 就可以完成整个编译过程. 本文面向一简单的代码结构,说明Makefile的编写,从而实现编译过程的自动化.

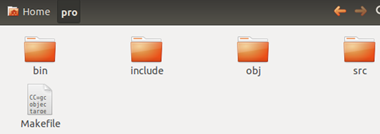

图1 代码结构

图1所示为代码结构, 文件夹src存放main.c, add.c, sub.c, mul.c和div.c等c源代码文件, common.h文件放在include目录, 生成的中间文件放在obj目录(编译过程中生成),最终编译成功的可执行文件放在bin目录。源代码中的main.c是程序的入口, 其调用add.c, sub.c, mul.c和div.c中的四个函数, 关于函数的声明都放置在common.h中.另外,要求Makefile中提供clean选项,只要输入命令”make clean”,可以将所有生成的.o文件和可执行文件删除。

满足上述要求的Makefile脚本:

1 | CC=gcc |

简要说明下,上述脚本中的特殊符号

1 | "$@": 表示目标文件; |

将上述内容的Makefile脚本放置到src文件夹所在的目录,然后在命令行端敲击make命令,回车即可. 图2是windows下模拟linux的Cygwin系统下运行Makefile脚本后的结果.

图2 Makefile执行后的效果

C语言代码和Makefile脚本下载链接如下:

https://github.com/tfzhang55/testmkfile